# **Policy Brief**

# Tracing the Emergence of Extreme Ultraviolet Lithography

Lessons for Identifying,

Protecting, and Promoting the

Next Emerging Technology

**Author**John VerWey

### **Executive Summary**

This paper presents a case study on the most important technology to have emerged in the past decade: extreme ultraviolet (EUV) lithography. In 2019, when the first commercial electronics enabled by EUV were released, the technology was hailed as "the machine that saved Moore's Law." All of today's most advanced artificial intelligence (AI) chips, smartphones, autonomous driving systems, and high-performance computers contain semiconductors fabricated using EUV lithography. The Dutch company ASML has emerged as the sole supplier of EUV machines, winning a 30-year race that granted the company a monopoly on selling the tool essential for fabricating leading-edge semiconductors.<sup>2</sup>

However, while ASML gets well-deserved praise for developing and commercializing EUV, this paper's focus is on the research community that supported EUV from the beginning: the academics in Japan, the United States, and Europe; the public-private partnerships; the conferences; and the industry collaboration that laid the groundwork for EUV in the 1980s and 1990s. Without this community, "the most technically advanced tool of any kind that's ever been made" would not have been possible. This paper traces the academic, government, and industry actors involved in a multi-decade moon-shot project that ultimately saw EUV ascend from a speculative emerging technology to the mechanism that makes Nvidia's leading-edge AI training chips and Apple's latest smartphone possible.

Careful study of the research community that supported EUV development is particularly relevant for policymakers and the semiconductor industry today. EUV research began in the 1980s, when the U.S. semiconductor industry was trying to fend off ascendent Japanese firms amid significant government intervention on both sides. At the same time, the industry recognized that a new generation of lithographic light sources would be necessary to fabricate future advanced chips to maintain Moore's law. Similar circumstances exist today, with policymakers in the United States, Europe, and Asia engaged in once-in-a-generation efforts to protect and promote their respective semiconductor industries, all while ascendent Chinese firms attempt to challenge industry leaders. Meanwhile, the entire semiconductor industry recognizes a slow-moving existential crisis: rapid advances in Al must be sustained by correspondingly rapid advances in computational power. However, the end of Moore's law is in sight, and not even EUV can save it.<sup>4</sup>

The development of EUV reflects many of the emerging technology themes observed in previous CSET analyses.<sup>5</sup> Research collaboration among academia, industry, and government has occurred for decades, making progress on associated technologies in

fields such as materials science, plasma physics, and chemistry. This progress has been documented in the form of journal article publications, patent filings, and conference proceedings. Over time, specific technologies would transition from government labs to the private sector, frequently through public-private partnerships and consortia formed to address and overcome technical hurdles. Eventually a private firm would assess a market opportunity, make investments to increase the technology's maturity, collaborate with customers, and commercialize the technology. Government support has always been essential at various points along the way.

Bibliometric study of the EUV research community during the period when EUV was still "emerging" offers important lessons for policymakers interested in identifying promising technologies today. It shows how academic research translates into scientific advances, the role of government and corporate labs, how international research collaborations accelerate innovation, the power of public-private partnerships, and the need for large amounts of patient private-sector capital. This paper catalogs this multi-decade path of innovation, identifying inflection points, signals, and sub-innovations along the way. Based on these findings, this paper concludes by introducing a set of criteria policymakers could use when attempting to identify future emerging technologies.

That a Dutch company, ASML, commercialized a technology pioneered in America's national laboratory ecosystem and largely funded by Intel also has important lessons for policymakers interested in protecting and promoting the next emerging technology. International collaboration on emerging technologies is inevitable, and guardrails on this collaboration come with trade-offs. Investments are an important source of funding for innovation, yet strategic acquisitions can fundamentally alter competitive dynamics in heavily consolidated industries. Finally, emerging technology supply chains evolve and mature in the private sector, whose incentives are profit and reliability, not geostrategic competitiveness. EUV tools are monopolized, but the EUV research community and underlying supply chain is globalized.

## **Table of Contents**

| Executive Summary                                                         | 1  |

|---------------------------------------------------------------------------|----|

| Table of Contents                                                         | 3  |

| Introduction                                                              | 4  |

| Background on Lithography and EUV                                         | 4  |

| The Development of EUV                                                    | 7  |

| EUV Origins                                                               | 9  |

| Fundamental Research and Technology Demonstration (1981–1992)             | 10 |

| Applied Research and Technology Development (1993–1997)                   | 11 |

| Consortia and Industry-Led Technology Maturation (1997–2009)              | 12 |

| Collaboration: Consortium Formation and the Global Research Agenda        | 12 |

| Competition: Emerging EUV Leadership                                      | 15 |

| Commercialization and High-Volume Manufacturing (2010–Present)            | 19 |

| The EUV Research Community: Characterizing Signals of Emergence           | 21 |

| Research Community Composition and Participation                          | 21 |

| Research Community Publications and Technical Areas of Focus              | 22 |

| Identifying, Protecting, and Promoting the Next Emerging Technology       | 24 |

| Identifying the Next Emerging Technology                                  | 24 |

| Protecting and Promoting the Next Emerging Technology                     | 26 |

| Promoting Emerging Technology                                             | 27 |

| Protecting Emerging Technology                                            | 28 |

| Conclusion                                                                | 30 |

| Author                                                                    | 31 |

| Acknowledgments                                                           | 31 |

| Appendix 1. Emerging Technology Attributes                                | 32 |

| Appendix 2. Next-Generation Lithography and Light Sources                 | 33 |

| Appendix 3. Comparing EUV Publication Intensity between SPIE and Scopus/V |    |

| Endnotes                                                                  | 37 |

### Introduction

### Background on Lithography and EUV

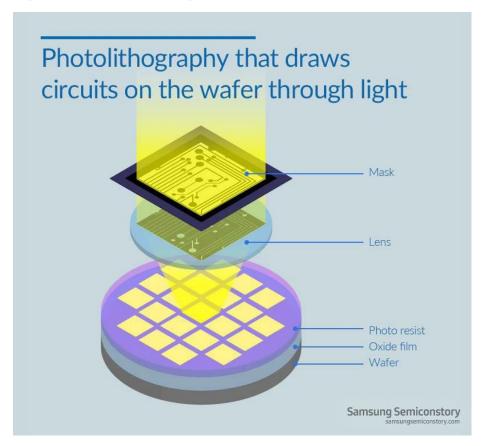

Extreme ultraviolet (EUV) lithography is the latest innovation in a long line of technical accomplishments that have supported the semiconductor industry's adherence to Moore's law from the 1960s to present.<sup>7</sup> In semiconductor fabrication, lithography is the process of imprinting circuitry on silicon wafers using light-sensitive chemicals. The technology functions much like the process of developing a photograph: Light is filtered through an image (a "mask" in industry jargon) containing a circuit pattern. That pattern is projected onto the wafer, which is covered in light-sensitive chemicals ("photoresist"). The light interacts with the materials on the wafer surface, depositing the pattern as desired. This process is repeated dozens of times before the desired circuit pattern is fabricated on the wafer (Figure 1).

Figure 1. The Photolithography Process

Source: Samsung, "Part 4, Drawing Structures in Nano-Scale," September 22, 2017, <a href="https://semiconductor.samsung.com/support/tools-resources/fabrication-process/eight-essential-semiconductor-fabrication-processes-part-4-photolithography-laying-the-blueprint/">https://semiconductor.samsung.com/support/tools-resources/fabrication-process/eight-essential-semiconductor-fabrication-processes-part-4-photolithography-laying-the-blueprint/</a>.

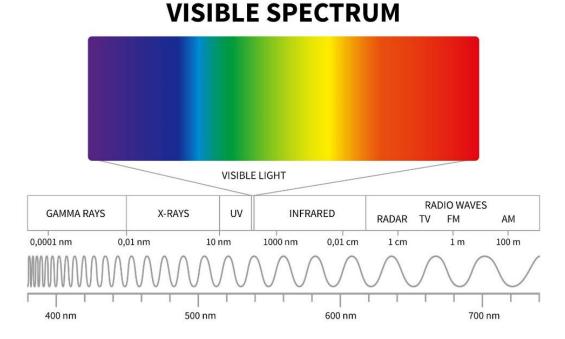

This lithographic process was first developed for use in the semiconductor industry at Fairchild Semiconductor and Texas Instruments in the late 1950s.<sup>8</sup> Over time, as circuits shrank to the nanometer level, the industry was forced to adopt unique lithographic-specific light sources and associated technologies, because the visible spectrum of light exceeded the width of the desired circuit patterns. Specialty light sources were introduced, allowing for deep ultraviolet (DUV) lithography. However, the limits of DUV technology were well understood as early as the 1980s.<sup>9</sup> Knowing the complexity of the task at hand, the semiconductor industry began to explore the scientific and technical merits of next-generation lithography (NGL) for fabricating advanced microelectronics decades before it would be necessary.

EUV lithography represents a departure from earlier photolithography approaches used by the semiconductor industry in several important respects, particularly the light source. EUV lithography functions by using high-powered lasers to incinerate 50,000 tin drops (each of which measures 30 micrometers, or 30-millionths of a meter) per second to generate extreme ultraviolet light. Because EUV light is absorbed by both air and glass, special mirrors, among the most flawless (as in, blemish-free) materials ever produced, then guide this light through masks and onto wafers in a vacuum chamber. Ultimately, this process imparts the ultrafine circuitry necessary for today's most advanced semiconductors (Figure 2).

First scanner Handler for moving Active mask is exposed to EUV light and storing masks mirror ASML Mask entrance and exit Track system attached to EUV scanner coats wafers before exposure and handles wafers after exposure Vacuum Handler for moving Wafer is Wafer is **EUV** light and storing masks measured exposed source

Figure 2. A Cross-Section Representation of an EUV Machine

Source: Maarten Steinbuch, Tom Oomen, and Hans Vermeulen, "Motion Control, Mechatronics Design, and Moore's Law," *IEEJ Journal of Industry Applications* 12, no. 2 (2022), <a href="https://www.jstage.jst.go.jp/article/ieejjia/11/2/11\_21006010/\_article">www.jstage.jst.go.jp/article/ieejjia/11/2/11\_21006010/\_article</a>.

Five thousand suppliers provide 100,000 parts, 3,000 cables, 40,000 bolts, and two kilometers of hosing to make an EUV tool. The tool weighs about 180,000 kilograms (200 tons), and ships in 40 containers spread over 20 trucks and three cargo planes. ASML reportedly only makes 15 percent of the EUV tool in-house, partnering strategically with firms worldwide to source the highest quality components. This has resulted in a uniquely international product that is Dutch in name only. Though ASML does not talk in detail publicly about its suppliers and the EUV supply chain, Table 1 presents a list of recent known suppliers of specific EUV subcomponents.

Table 1. Summary of Notable EUV Subcomponents and Suppliers

| Component        | Subcomponent                                                       | Supplier(s)                                                                            |  |  |

|------------------|--------------------------------------------------------------------|----------------------------------------------------------------------------------------|--|--|

|                  | Deposition                                                         | Veeco (U.S.), Applied Materials (U.S.)                                                 |  |  |

| Mask Blanks      | Inspection                                                         | KLA (U.S.), Lasertec (Japan)                                                           |  |  |

|                  | Blanks                                                             | AGC (Japan), Hoya Group (Japan)                                                        |  |  |

|                  | Patterning                                                         | IMS Nanofabrication (Austria), NuFlare Technology (Japan), JEOL (Japan)                |  |  |

|                  | Etching                                                            | Applied Materials (U.S.), Tokyo Electron (Japan)                                       |  |  |

| Mask             | Cleaning                                                           | SUSS MicroTec (Germany), Applied Materials (U.S.), SCREEN (Japan)                      |  |  |

| Patterning       | Inspection                                                         | KLA (U.S.), HMI (U.S., owned by ASML), NuFlare Technology (Japan),<br>Lasertec (Japan) |  |  |

|                  | Defect Review                                                      | Lasertec (Japan), Zeiss (Germany)                                                      |  |  |

|                  | Repair                                                             | Zeiss (Germany), RAVE (U.S., owned by Bruker), Hitachi (Japan)                         |  |  |

| _                | Pellicles                                                          | ASML (Netherlands), Teledyne DALSA (Canada), S&S Tech (South Korea)                    |  |  |

| Mask<br>Handling | Mask Pod                                                           | Entegris (U.S.), Gudeng Precision (Taiwan)                                             |  |  |

| Handing          | Coaters and Developers                                             | Tokyo Electron (Japan), Lam Research (U.S.)                                            |  |  |

| Photoresist      | JSR (Japan), Shin-Etsu Chemical (Japan), Tokyo Ohka Kogyo (Japan), |                                                                                        |  |  |

| Optics           | Mirrors                                                            | Zeiss (Germany), Berliner Glas (Germany, owned by ASML)                                |  |  |

| Light Course     | Laser                                                              | Cymer (U.S., owned by ASML), TRUMPF (Germany)                                          |  |  |

| Light Source     | Vessel                                                             | VDL Enabling Technologies (Netherlands)                                                |  |  |

| Wafer            | Wafer Handling                                                     | VDL Enabling Technologies (Netherlands), Berliner Glas (Germany, owned by ASML)        |  |  |

| Handling         | Metrology                                                          | HENSOLDT (Germany), ASML (Netherlands)                                                 |  |  |

Source: Author's compilation. 14

EUV tools are so essential to the semiconductor industry that ASML has become a technology industry leader: companies that can afford an EUV tool, which reportedly costs \$350 million as of 2023, are able to make the most advanced chips in the world. Companies that cannot afford EUV tools (or must wait while the back orders are cleared) settle for making second-best chips. This role has also put ASML in the middle of geopolitical tensions. Chinese firms, eager to make the world's most advanced electronics, are currently blocked from purchasing EUV tools on national security grounds by the Netherlands.

### The Development of EUV

The following sections describe the development of EUV from chronological and bibliometric perspectives. EUV development occurred in academic labs, corporate

research and development (R&D) facilities, private firms, and public-private partnerships over the course of 30 years. First, the chronological history of the EUV development program is presented, highlighting key contributions from academia, government, and industry, as well as the collective technical obstacles they worked to overcome.

Second is a bibliometric analysis of the EUV research agenda over the course of 30 years. Much of EUV lithography's development occurred in the public record in the form of publications, conference proceedings, and patent filings. The analysis is derived from a book by the Society of Photo-Optical Instrumentation Engineers (SPIE), *EUV Lithography*, published in 2008 and revised in 2018.<sup>17</sup> This manual presents a history of EUV's development from a technical perspective and was largely written by the key contributors active in the research community from the 1980s to the present. Importantly, it provides a comprehensive list of the consequential publications, actors, and narrative history.

This bibliometric analysis focuses on the EUV research community's accomplishments during the 30-year period when EUV was an emerging technology. The analysis demonstrates specific inflection points and accomplishments along the way that can be used as signals to identify other technologies that may be emerging today. It also reviews policymaker options for protecting and promoting emerging technologies at these inflection points.

### **EUV Origins**

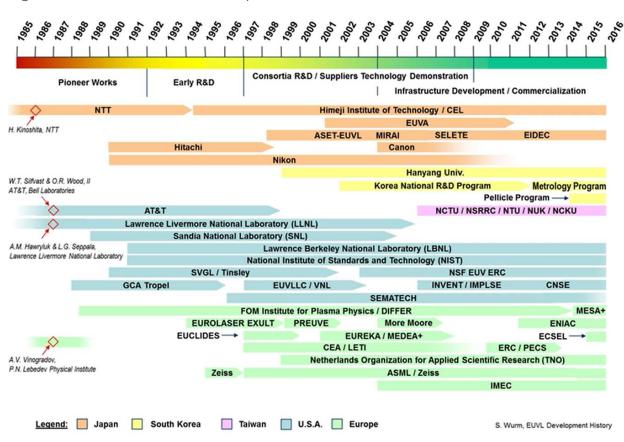

The first period of EUV research was focused on demonstrating the technical promise and feasibility of using soft X-ray projection lithography (SXPL) in semiconductor fabrication. The next period focused on developing the imaging systems and system integration, and identifying technical barriers and potential "showstoppers." From the late 1990s through 2010, industry stepped in and focused the EUV research agenda on system development in preparation for high-volume manufacturing (Figure 3). From 2010 to the present, ASML has emerged as the sole supplier of EUV systems, successfully shipping its first allegedly "production-ready" EUV lithography tools in 2013. However, it was not until 2019 that the first electronic devices containing EUV-enabled semiconductors became available.

Figure 3. Timeline of EUV Development and Notable Actors

Source: Nelson M. Felix and David T. Attwood Jr., "EUV Lithography Perspective: From the Beginning to HVM (Conference Presentation)," SPIE Advanced Lithography, San Jose, California, 2020, video, 75:00, April 28, 2020, <a href="https://www.spiedigitallibrary.org/conference-proceedings-of-spie/11323/2572271/EUV-Lithography-Perspective--from-the-beginning-to-HVM-Conference/10.1117/12.2572271.full#\_=\_.</a>

### Fundamental Research and Technology Demonstration (1981–1992)

Soft X-ray reduction imaging, the technology that would later become EUV, was an idea ahead of its time. When, in 1981, researchers in the United States first started investigating whether soft X-rays could be used to impart images, their efforts focused on applications related to X-ray microscopes and X-ray telescopes. In fact, some of the very first tests evaluating soft X-rays for imaging were conducted at the Marshall Space Flight Center in Huntsville, Alabama. At this time, the leading NGL technology was X-ray proximity lithography (XPL). IBM in the United States and NTT in Japan were actively evaluating XPL for semiconductor device production, though both companies would later abandon the technology once manufacturing problems with XPL masks were deemed unresolvable.

Hiroo Kinoshita, an employee at NTT who emerged as a leading figure in the EUV lithography community, first began considering the applicability of this pioneering research for semiconductor device fabrication in 1984.<sup>21</sup> Calling his approach X-ray reduction lithography, Kinoshita presented his initial findings at the Japan Society of Applied Physics in 1986 to little acclaim: the audience "seemed unwilling to believe that an image had actually been made by bending x rays."<sup>22</sup> Researchers in the United States experienced similarly negative feedback initially. Employees at AT&T Bell Laboratories approached the U.S. government in 1986, suggesting that soft X-ray lasers, paired with multilayer reflectors, could serve as a practical NGL tool. The proposal they prepared for the U.S. government received an "extremely negative" review, with the reviewers going so far as to say, "The printing of 0.1 [micron] features...would never be needed for [silicon] integrated circuits."<sup>23</sup>

By 1988, researchers at Lawrence Livermore National Laboratory (LLNL), part of the U.S. Department of Energy (DOE) national laboratory system, had picked up on Kinoshita's research and proposed the first SXPL system.<sup>24</sup> These researchers, all of whom were affiliated with LLNL's laser fusion program, took this pioneering research one step further, fabricating components and developing techniques to conduct diagnostics to verify SXPL's promise.<sup>25</sup> Kinoshita's research aligned with these efforts, and in 1989 he published a paper that proposed optimal SXPL exposure wavelengths, photomasks, and photoresist.<sup>26</sup> By the early 1990s, researchers at Sandia National Laboratories (SNL), another of the DOE's national labs, had partnered with AT&T Bell Labs to demonstrate the first SXPL system with a laser plasma source. Momentum in the United States continued to grow as the U.S. Defense Advanced Research Projects Agency (DARPA) kicked off its advanced lithography program in 1991.<sup>27</sup> Soon thereafter, Kinoshita and several Japanese colleagues presented a refined, and

technically promising, two-mirror imaging system using SXPL in partnership with Tinsley Laboratories, a U.S. firm responsible for the optics used in the Hubble Space Telescope.<sup>28</sup> Finally, in 1992, Intel CEO Andy Grove approved a \$200 million company-internal R&D investment into EUV lithography.<sup>29</sup>

### Applied Research and Technology Development (1993–1997)

The second phase of R&D began with a name change: in 1993 the SXPL research community decided to coalesce on the term "extreme ultraviolet lithography." This decision had several motivations. First, the term EUV distinguished this approach from the XPL research still being explored by IBM and NTT at the time. Additionally, EUV sounded like an extension of DUV, the most common form of optical lithography then in use (Appendix 2 has more information on each of these lithographic approaches). The adoption of the term also served to remove the association with X-ray lithography (which didn't work) and create an association with DUV lithography (which did work).

The U.S. National EUV Lithography Program emerged in 1994. Consisting of researchers from LLNL, SNL, Lawrence Berkeley National Laboratory (LBNL), and AT&T Bell Labs, this program was funded by DOE and steered by a technical advisory group with DARPA, DOE, and industry representatives. Teams at LLNL and SNL began developing imaging systems and the first tool leveraging EUV technology capable of precise overlay.<sup>33</sup>

Development of mirror imaging systems (the "optics") was a major focus of research during this period, with teams at SNL, Tropel Corporation, AT&T Bell Labs, and Silicon Valley Group (SVG) Lithography Systems all contributing to advances in the United States.<sup>34</sup> Related research in Japan continued to be led by NTT, with increasing participation from Hitachi and Nikon.<sup>35</sup>

European research into EUV lithography also began in earnest during this period. Notably, an EUV research program called EXULT—which counted among its members ASM Lithography, the FOM Institute for Atomic and Molecular Physics, Sopra, Carl Zeiss AG, and Delft University of Technology—began a research agenda focused on "high-power debris-free [light] sources, precision optics fabrication and metrology, and defect-free masks."<sup>36</sup> Europe's first EUV workshop was organized and hosted by Zeiss in 1995.<sup>37</sup> The concentration of EUV research in the Netherlands at this time was notable. The Netherlands was seen by both the U.S. and Japanese semiconductor industries, which were at the time engaged in fierce competition, as neutral ground.<sup>38</sup> As a result, companies in Japan and the United States collaborated closely with

European firms. This head start would serve as a boost to an emerging Dutch company then known as ASM Lithography (later ASML).

### Consortia and Industry-Led Technology Maturation (1997–2009)

By the mid-1990s, the International Technology Roadmap for Semiconductors forecast that a new lithography technology would need to be ready for high-volume manufacturing by 2005 if the industry was to keep pace with Moore's law.<sup>39</sup> However, despite years of exploratory work into XPL (led by IBM in the United States), projection electron and ion beams (led by AT&T Bell Labs in the United States), and shorter DUV wavelengths, no promising candidate technology had emerged.<sup>40</sup> At this inflection point, DOE's funding for the National EUV Lithography Program ended. This decision, the result of broader DOE budget reductions in the 1990s, occurred at a time when it was clear to industry that, if anything, the EUV lithography research agenda required ever greater funding.

The decision to cease funding the National EUV Lithography Program prompted Intel to step in and provide "bridge funding" to keep the U.S. EUV R&D community together until a more extensive program could be developed. In 1997, EUV LLC, led by Intel, was formed to push this research agenda forward in the United States. EUV LLC quickly established a contract with DOE through a novel national virtual laboratory (NVL) structure to ensure close alignment with the research teams at LLNL, LBNL, and SNL already engaged in EUV research.

Following the creation of EUV LLC in the United States, related consortia in Japan and Europe soon appeared. In 1998, the Japanese Association of Super-Advanced Electronics Technologies (ASET) established an EUV research agenda, and Europe's Extreme UV Concept Lithography Development System (EUCLIDES) was formed.<sup>43</sup> Unlike the U.S. government, the Japanese government and the European Commission provided direct financial support to these EUV research agendas.<sup>44</sup>

### Collaboration: Consortium Formation and the Global Research Agenda

With the creation of these public-private consortia in the United States, Europe, and Japan in 1997 and 1998, the semiconductor industry began to pursue EUV research in a much more concerted manner. Each of these consortia competed and collaborated in their efforts to commercialize EUV lithography systems. Recognizing the magnitude of the tasks at hand, the consortia established multiphase research agendas. While there was substantial overlap among the technical research agendas of the three consortia,

each of them expected that production-ready tools would not be available until the mid-2000s at the earliest.

Beginning in 1999, an annual international EUV workshop was held, rotating between the United States, Japan, and Europe. The function of this workshop, as well as other industry conferences and exchanges, served to advance overall progress on EUV research by sharing the results of their Phase I efforts (described below). Each consortium expected that Phase I would take three years and follow-on efforts aimed at developing a commercial tool would take a minimum of another three years, with EUV LLC aiming for a fab-ready system "on the floor in 2004."

### Japan, ASET, and EUVDA

Japan's EUV research program at ASET conceived of a nine-year research agenda culminating with commercial tools ready for use in the mid-2000s. The program focused on three lines of effort in Phase I: the exposure system (including mirrors, the light source, and the mechanical system), multilayer masks (including mask patterning and defect detection), and photoresist development. ASET's research agenda was coordinated by Hiroo Kinoshita (who by this time had departed NTT for the Himeji Institute of Technology), with participation from 10 semiconductor manufacturers and two equipment suppliers.<sup>45</sup>

In some respects, Japan had a head start in NGL research: Japanese firms Canon and Nikon, who led in worldwide lithography sales in the mid-1990s, were pursuing company-internal NGL development efforts as well. <sup>46</sup> Canon had invested heavily into XPL, while Nikon had bet on electron-projection lithography (EPL). However, by late 2000, Canon had announced it would cease its XPL research in 2001. <sup>47</sup> The company argued that this line of research could be repurposed, giving it a head start in EUV work, while Nikon continued investigating EPL and EUV simultaneously. <sup>48</sup> Japanese firms and consortia continued to experience halting progress in EUV and other NGL technologies, which ultimately encouraged closer collaboration and technical exchanges between ASET and EUV LLC in 2001. <sup>49</sup>

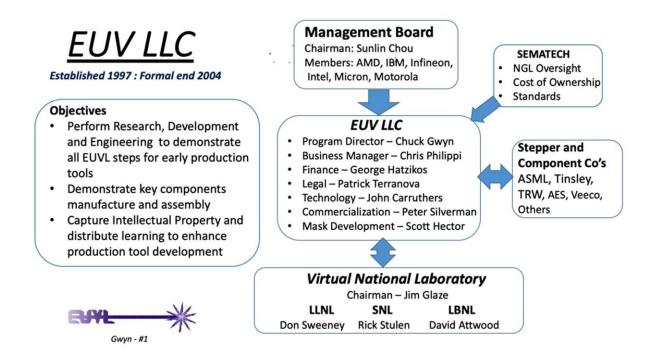

### The United States and EUV LLC

The EUV LLC research agenda was the most well funded and ambitious of the three consortia. In Phase I, EUV LLC identified EUV optics, multilayer coating, metrology, masks, light source, photoresist, and development of an engineering test stand (a prototype EUV system) as "major tasks." More important than funding was the level of participation from industry during this period: in addition to the aforementioned DOE

labs and Intel, ASML, Motorola, AMD, Micron, Infineon Technologies AG, and IBM ultimately joined EUV LLC (Figure 4).<sup>50</sup> No company was more committed to EUV research during this period than Intel. Preliminary estimates from Intel and the national lab partners in EUV LLC put an annual budget at around \$60 million, a number that would swell into the billions in the coming decade as Intel committed "what felt like infinite money for solving an impossible problem."<sup>51</sup>

Figure 4. EUV LLC Structure

Source: Felix and Attwood, "EUV Lithography Perspective," 37:30.

Intel and its EUV LLC partners ended up committing \$250 million to the DOE labs in 1997. Remarkably, Intel agreed to pay 100 percent of the national labs' EUV research costs through a Cooperative Research and Development Agreement (CRADA) with the NVL that was hailed by the then secretary of energy as "the biggest investment the private sector has ever made in the Department of Energy." Intel's return on this investment was access to the 100-plus researchers in the DOE national labs engaged in EUV work, the rights to all EUV-affiliated intellectual property (IP) generated under the auspices of EUV LLC, and the (hopeful) continuation of Moore's law. DOE retained royalty-free right to use EUV-affiliated technologies generated by EUV LLC for defense applications.

### Europe, ASML, and EUCLIDES

Led by ASML in partnership with Carl Zeiss AG and Oxford Instruments, Europe's EUCLIDES program focused its research efforts on mirror substrates, high-reflectivity multilayer coatings, and vacuum stages, while also evaluating plasma and synchrotron light sources.<sup>55</sup> EUCLIDES' progress in Phase I required access to industry know-how, applied R&D, and government user facilities and test beds. ASML chose to partner with TNO TPD, a Dutch institute for applied R&D; FOM Rijnhuizen, a Dutch research institute for plasma physics; PTB, the German metrology institute; and Fraunhofer IWS, a German institute for applied R&D focused on materials science and lasers.<sup>56</sup>

The European research agenda into EUV was relatively small compared to the U.S. and Japanese efforts, yet it showed early signs of progress. Notably, Zeiss (the firm that today supplies all of the optics for ASML's EUV tools), in collaboration with Fraunhofer IWS, started to see early breakthroughs on the multilayer coating challenges in 2000.<sup>57</sup> Early on, ASML recognized it would need to rely on an extensive supply chain for many of the components and subcomponents as opposed to doing everything inhouse.<sup>58</sup> Based on EUCLIDES' initial progress, in 2001 ASML "assigned a small group of people and modest resources to build a prototype EUV system." This goal, which took five more years to realize, was aided by ASML's partnership with EUV LLC beginning in 1999.

### **Competition: Emerging EUV Leadership**

During this period, in addition to the cooperative research agenda outlined in the previous section, there remained intense competition between countries, NGL technologies, and the companies championing them.

### **Competing Countries**

The first question the secretary of energy fielded after announcing the formation of EUV LLC in 1997 was from a reporter who asked what steps the DOE was taking to ensure "American equipment manufacturers will benefit from this program and that it won't serve to perpetuate the dominance of Japanese equipment manufacturers in lithography technology." At the time, the Japanese semiconductor industry was ascendent, and U.S. semiconductor firms were keen to maintain (and in some cases regain) their leading position. The U.S. government had anticipated this potentially controversial point and included an article in the agreement governing EUV LLC that established a "net U.S. benefit" clause, essentially requiring that participants commit to using EUV LLC-derived IP in support of U.S. manufacturing. Writing retrospectively,

the former head of EUV LLC stated, "The early failure to recognize that the U.S. government would prevent the EUV LLC from licensing lithography suppliers in Japan prevented the development of a robust competitive environment for [EUV]." Nevertheless, the industry recognized that the scale of the technical challenges necessitated closer international coordination. With Japanese collaboration politically unpalatable, EUV LLC looked to European partners.

In 1999, EUV LLC entered into an agreement with ASML that formalized the company's participation in the consortium, closely aligning the work of EUCLIDES with U.S. efforts. <sup>62</sup> Inclusion of this non-U.S. member firm was motivated by Intel, which had pushed for ASML's participation as a means of accelerating research progress. <sup>63</sup> ASML's inclusion in EUV LLC came over objections from some in the U.S. government who expressed concern that including non-U.S. partners in the LLC could result in the transfer of taxpayer-funded IP to a non-U.S. company. In exchange for membership in EUV LLC, ASML promised to build a factory in the United States comparable in scale to its Netherlands facility, agreed that 55 percent of the components in its future commercial EUV systems would be sourced from U.S. suppliers, and committed to sharing EUV technologies derived from the EUCLIDES program. <sup>64</sup> Soon thereafter, German firm Infineon Technologies AG also negotiated access to EUV LLC, offering to pay \$10 million, over objections from the U.S. Department of Commerce. <sup>65</sup>

### **Competing Technologies**

At least four NGL technologies were seriously considered by the semiconductor industry and championed by specific firms before EUV emerged as the clear winner (see Appendix 2 for more information). Each of these NGL approaches faced technical and economic obstacles. A complete lithography system requires (1) the exposure tool; (2) mask making, mask equipment, and mask materials; (3) the photoresist materials and processing equipment; and (4) metrology equipment for critical dimension and overlay. Geological Significant technical innovation was required for each of these subcomponents and functions. In almost all cases, though, economic considerations dictated the rise and fall of different NGL approaches. Ultimately, these tools needed to be able to conduct hundreds of wafer exposures per hour (referred to as "throughput"), with as little downtime as possible, for years at a time. NGL technologies that lacked throughput and reliability did not prove economically viable.

SEMATECH, a nonprofit consortium founded in 1987 to sustain U.S. semiconductor industry leadership, convened an NGL task force in 1997 that identified XPL, EPL, and ion projection lithography as the most likely candidates (each are described further in Appendix 2).<sup>67</sup> EUV came in fourth place. Nevertheless, ASML's participation in EUV

LLC in 1999 accelerated enthusiasm for EUV lithography at the expense of the other lithographic approaches then under consideration. Less than two years later, in early 2001, ASML dissolved eLith LLC, a joint venture with U.S. firm Applied Materials that had been focused on developing a next-generation EPL tool derived from research at AT&T Bell Labs.<sup>68</sup> In making the decision to abandon EPL, ASML cited EUV's promise as a "more extensible" technology—offering manufacturing capabilities for multiple generations of processor technology—as well as EPL's relatively lower throughput.<sup>69</sup>

In 2002, ASET reported an alpha prototype EUV tool capable of fabricating chips at the 35nm node. That same year, Japanese firms, with the support of Japan's Ministry of Economy, Trade, and Industry, established the Extreme Ultraviolet Lithography System Development Association (EUVA). Membership in EUVA consisted of all the leading Japanese semiconductor firms: Canon and Nikon; light-source manufacturers Komatsu, Ushio, and Gigaphoton; and device manufacturers Fujitsu, NEC, Renesas Technology, and Toshiba. ASET focused on developing mask and resist technology, while EUVA and its leading members Nikon and Canon focused on optics and exposure tool ("scanner") development. Despite making progress in these areas, by 2003 Japan's efforts in EUV were already being characterized as "play[ing] catch up."

Part of the reason Japanese firms were perceived to be falling behind in EUV was the success of U.S. efforts under EUV LLC. The consortium, which ceased operations in 2004, resolved many of the major tasks initially identified in 1997 and delivered the first prototype EUV lithography tool, referred to as the engineering test stand. Its six-year research effort is generally regarded as a success. Yet, substantial technical hurdles remained by the time of EUV LLC's dissolution, and its expected delivery of an alpha tool "on the floor in 2004" was now delayed several years further. At this point, SEMATECH stepped into the void left by EUV LLC. SEMATECH focused on EUV commercialization efforts, building infrastructure to support production of EUV mask blanks and photoresist, providing light-source data, and characterizing optics lifetime and contamination.<sup>75</sup>

This delay did not cause an end to Moore's law as the International Technology Roadmap for Semiconductors had earlier predicted, primarily because of successful technical innovations that extended DUV lithography to fabricate all the way down to the 45nm node and below. Using DUV lithography for more advanced device fabrication is slower and more resource intensive (more masks and photoresist are required, increasing costs and the possibility of defects) but technically viable. ASML now estimates that, while it takes only nine EUV lithography steps to fabricate a 7nm chip, DUV lithography tools can accomplish the same task in 34 steps.

As early as 1999, the industry recognized that DUV extension could be viable, and by the early 2000s DUV lithography's successful extension actually reduced the urgency of the EUV research agenda. By the mid-2000s, only hard problems remained: it had become apparent to the industry that EUV technology would not be ready until the end of the decade, if ever. Key technical issues were not being resolved in a timely manner, delaying the project writ large. These issues included "[light] source output power and lifetime; availability of defect-free masks; reticle protection during storage, handling and use; projection and illuminator optics lifetime; resist resolution, sensitivity and line width reduction; and optical quality for the 32-nm node. Place 1920, these ongoing technical hurdles led several researchers to declare that EUV lithography was headed for failure, with one keynote speaker predicting, No one will ever print a wafer for profit with EUV. This same year, DARPA ended funding for its advanced lithography program, estimating it had spent \$1 billion over the program's 14-year existence.

### **Competing Companies**

In 2000, ASML, then the second largest lithography company in the world, made an offer to acquire SVG Lithography, the fourth largest. The acquisition—which was approved in 2001 after an extensive national security review process in the United States that forced ASML to divest SVG's Tinsley Labs business—made ASML the largest lithography vendor in the world, putting it ahead of Canon and Nikon.<sup>82</sup> Importantly, the purchase of SVG also gave ASML the inside track to win future business from Intel, which had historically relied on SVG for lithography tools.<sup>83</sup> With SVG's acquisition, however, the last American lithography-tool supplier ceased to exist.<sup>84</sup> Not long after, Northrop Grumman made an offer for TRW, a firm supporting EUV LLC's work on light sources, and, subsequent to the closing of the transaction, exited light-source development. Northrop Grumman ended up donating all of its EUV-affiliated IP to the University of Central Florida in 2004.<sup>85</sup>

These acquisitions came at a fraught time for the semiconductor industry. Global semiconductor sales fell 32 percent following the dot-com crash in 2001 and recovered slowly from 2002 to 2005, hurting firm profitability and thus R&D budgets. Gone bright spot was Intel, whose personal computer business proved resilient and exceedingly profitable. Intel used these profits creatively during the downturn, funding ongoing research into EUV at a time others could not afford to. In 2003, Intel purchased \$90 million worth of Nikon bonds, "partly to ensure Nikon climbed fully on board the EUV bandwagon." It invested another \$20 million in a San Diego-based developer of EUV light sources called Cymer to sustain its operations.

ASML and Nikon competed head-to-head for lithography market share in the mid-2000s, simultaneously pursuing different NGL technologies.<sup>89</sup> Adding to this competition, Nikon sued ASML for patent infringement in 2001 and reached a settlement three years later, with ASML and Zeiss paying \$87 million and \$58 million to Nikon respectively.<sup>90</sup> In spite of this win for Nikon, that same year it became increasingly apparent that its big bet on EPL was never going to reach the throughput necessary to be competitive with EUV. In 2005, it ceased efforts to commercialize EPL.<sup>91</sup>

ASML, Nikon, and Canon continued to guarantee EUV alpha tools to customers by the mid-2000s, with production-ready tools by 2009. In 2006, ASML shipped its first EUV prototype tools to Belgium's Interuniversity Microelectronics Centre (IMEC) and the College of Nanotechnology, Science, and Engineering (CNSE) in New York State. In 2007, Nikon reported that its first two EUV tools would be shipped to Intel and Selete (a Japanese joint venture). In 2008, CNSE successfully used ASML's demo tool to produce the world's first EUV test chips. Canon continued to struggle with EUV and by 2009 had decided to exit the race, leaving only ASML and Nikon as viable suppliers to the industry. That same year, it was rumored that Nikon's EUV program was experiencing further delays.

### Commercialization and High-Volume Manufacturing (2010–Present)

It was time to make money. ASML and Nikon had been taking orders for their long-delayed EUV tools for years, citing per-tool prices between \$15 million and \$20 million in 2001. But in 2010, ASML's first preproduction EUV system was finally shipped to a Samsung research facility in South Korea, and the cost had risen to \$120 million per tool. Be The costs of developing EUV had escalated to the point that Nikon elected to exit EUV lithography system development altogether in 2011, leaving ASML as the sole firm pursuing EUV. Set getting to this point had cost ASML tremendously, and it found itself strapped for cash just as the first EUV tools were being evaluated by its customers. In response, ASML announced a 2012 "customer coinvestment program," in which its most important customers—Samsung, Intel, and TSMC—would fund further EUV research and rollout in exchange for equity in ASML. Intel committed \$4 billion, while Samsung and TSMC each committed \$1 billion.

With this assurance, ASML doubled down on its efforts to commercialize EUV tools. The last major technical hurdle to be addressed had to do with the light source. In late 2012, ASML made an offer to acquire Cymer, the San Diego-based DUV and EUV

light-source developer, for \$2.5 billion to vertically integrate its supply chain further and accelerate progress.<sup>103</sup>

From this point forward, the story of EUV's emergence becomes much more well-known. The light-source challenges were resolved by ASML and Cymer, with critical help from the German laser manufacturer TRUMPF. In 2013, ASML shipped its first EUV production system, officially signaling the "emergence" of the technology, though it would not be ready for high-volume manufacturing in a leading-edge fab until Samsung and TSMC started shipping the first EUV-enabled products in 2019. 104 ASML's ascendence in the lithography world coincided with the decline of Japanese lithography firms, who today maintain about 10 percent of the worldwide lithography market, with ASML holding roughly 90 percent market share (and, of course, for EUV, 100 percent market share). 105

### The EUV Research Community: Characterizing Signals of Emergence

Throughout the timeline of events outlined in the previous section, the research community engaged in EUV commercialization was actively publishing, patenting, investing, and partnering on affiliated topics. This corpus of work provides a rich case study for researchers interested in identifying emerging technologies. Importantly, much of this information has already been collected and organized thanks to SPIE's definitive EUV Lithography volume. Using this book, it is possible to define the members of the research community and the discrete tasks on which they worked and to conduct analysis of this output over time to look for signals of emergence.

The analysis provided in this section is derived from SPIE's EUV Lithography. SPIE conferences were among the most important for the EUV research community in the 1990s and mid-2000s and provided a forum for researchers to share findings internationally. This volume, first published in 2008 and revised and republished in 2018, provides a comprehensive history of EUV development and an overview of each major subsystem, along with the technical hurdles overcome. The narrative of events, actors involved, and publications cited in the section that follow are extracted from this volume.

### Research Community Composition and Participation

Writing his history of EUV development from the 1980s through 1996, Hiroo Kinoshita lists about 300 researchers by name as having made "important contributions" to EUV lithography during this period. This group, though not an exhaustive list, likely represents the most comprehensive snapshot of the EUV research community from the 1980s through mid-1990s. The United States (about 225 researchers), Japan (about 45 researchers), and Europe (about 30 researchers) were home to this research community. Roughly 10 percent of researchers were affiliated with a university, 30 percent were affiliated with a government-supported research institution (i.e., a national laboratory), and the remaining 60 percent were employed in the semiconductor industry. 108

With the formation of the consortia in the late 1990s, the composition of this research community shifted decisively from academia to industry. The overall number of participants in Japan's ASET and EUVA research programs and in Europe's EUCLIDES program is more difficult to ascertain. However, over 2,800 individuals are listed as a coauthor on one or more publications in the SPIE's history of EUV, indicating the research community grew dramatically from the mid-1990s onward. This number is likely a conservative representation of worldwide participation in EUV research, as

many key contributors were employed by the industry at the time and not publishing on their work.

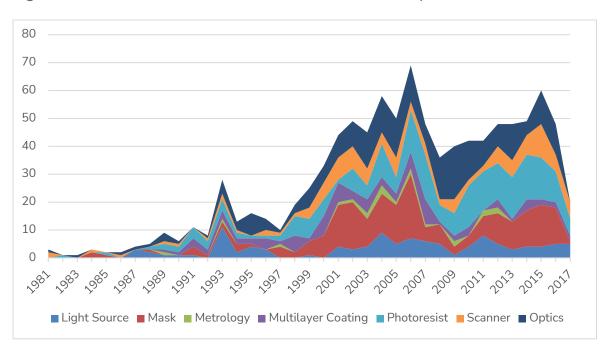

### Research Community Publications and Technical Areas of Focus

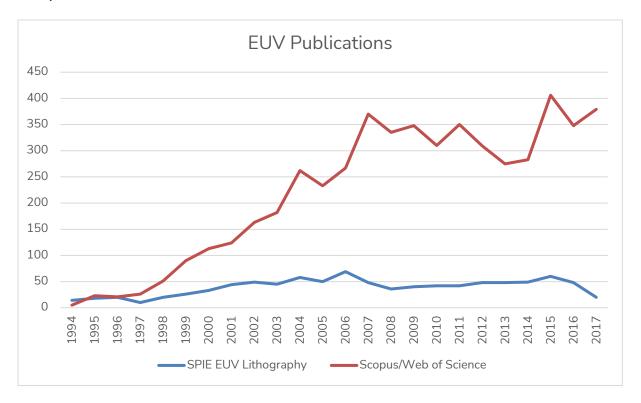

This research community publicly reported on progress and obstacles in the form of academic publications from the 1980s through the 2010s. Of the 1,035 distinct EUV-affiliated publications cited in the SPIE's volume, the vast majority of them were published from 1997 onward (Figure 5). Interestingly, there are two observable spikes in EUV-affiliated publications around 1993 (when the research agenda for EUV became more formalized) and again around 2006 (when ASML shipped its first alpha tools to IMEC and CNSE). Each of these periods was subsequently followed by a steep decline in publications, an EUV winter of sorts, when interest in (and perhaps enthusiasm for) the technology waned in the face of technical and economic obstacles. It

Figure 5. Number of EUV-Affiliated Publications Annually, 1981–2017

Source: Author's compilation, derived from Hiroo Kinoshita and Obert Wood, "EUV Lithography: An Historical Perspective," in *EUV Lithography*, ed. Vivek Bakshi (Bellingham, WA; SPIE, 2008), <a href="https://www.spiedigitallibrary.org/ebooks/PM/EUV-Lithography/1/EUV-Lithography-An-Historical-Perspective/10.1117/3.769214.ch1">https://www.spiedigitallibrary.org/ebooks/PM/EUV-Lithography/1/EUV-Lithography-An-Historical-Perspective/10.1117/3.769214.ch1</a>.

Among the technical areas that saw the most sustained research and publication output over time, photomasks, photoresist, and optics stand out. Each of these areas presented significant scientific and technical obstacles to the overall research agenda. Interestingly, the EUV light source, which was the last and most difficult obstacle to overcome, has a comparatively small publication footprint. This may be because the companies developing EUV light sources chose to keep that information as a trade secret during the period of development. This may also explain why EUV-affiliated metrology publications, a similarly remarkable technical accomplishment, are underrepresented.

The 1,035 publications cited in the SPIE volume represent a lower bound of the total EUV-affiliated publications from the 1980s to present. A simple query of "EUV lithography" in Scopus and Web of Science indicates a similar spike in interest from the 1997 period onward. However, Web of Science indicates an average of 248 EUV-affiliated publications per year (and a median of 267) from 1997 through 2017. This suggests that thousands of additional papers dealing with topics related to EUV lithography exist (see Appendix 3 for more information).

### Identifying, Protecting, and Promoting the Next Emerging Technology

The story of EUV shows that early government interventions matter most with respect to promoting emerging technologies, while government interventions to protect such technologies either come too late or lack relevance due to a limited tool kit. Interestingly, the moments when governments can make the most difference in promoting an emerging technology are the same moments when governments are most powerless to protect it. Conversely, by the time a technology is mature or "ready" enough to merit protection, there is very little policymakers can do to continue to promote its development, as it will most likely have "emerged" in the hands of industry.

Government efforts to identify emerging technologies are necessary but insufficient to protect and promote them. Though it may have been possible for policymakers to spot the emergence of EUV using some of these signals, the simple reality is that emerging technologies start out as arcane ideas championed by a small cohort of intensely passionate researchers. In general, policymakers lack the technical literacy, resources, and patience necessary to characterize and track a technology's emergence. Nonetheless, policymakers can use the template introduced in the next section to assist in identifying emerging technologies based on bibliometric and economic signals: publications and investments.

### Identifying the Next Emerging Technology

Previous CSET research has described the challenges and opportunities policymakers face when attempting to identify emerging technologies. <sup>113</sup> By definition, emerging technologies are new and rapidly changing, making them hard to track. Because these technologies are inherently immature, the underlying chain of people, processes, products, services, information, and resources that supports the technology is difficult to define. Additionally, technology development is diffuse and occurs in universities, firms, and government labs, often simultaneously and across borders.

"Emerging technology" as a concept also lacks an agreed-upon definition. For the purposes of this paper, an emerging technology is "a relatively fast growing and radically novel technology characterized by a certain degree of coherence persisting over time and with the potential to exert a considerable impact on socio-economic domain(s)."

114 Using publication data and investment trends described earlier in the paper, Table 2 presents a template researchers and policymakers could use to identify other emerging technologies by quantitatively assessing coherence and growth and

qualitatively assessing impact and novelty (more context on each of these attributes is in Appendix 1).

Table 2. Signals of Emerging Technology Coherence, Growth, Impact, and Novelty

|                                                                                                 | Coherence                                                                                                                                                                                                                                                                        | Growth                                                                                                                                                                                                                        | Impact                                                                                                                                                               | Novelty                                                                                                                       |

|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Publications                                                                                    | <ul> <li>&gt;100         contributors         (representing         25+         academic,         industry, and         government         institutions)</li> <li>A total of         50+         publications         annually for         a five-year         period</li> </ul> | <ul> <li>Number of contributors doubles in a five-year period, exceeding 500 individuals</li> <li>Number of publications increases 100% year over year for a five-year period, exceeding 100 publications annually</li> </ul> | Leading researchers are listed as inventors on patent filings                                                                                                        | A new annual conference series or journal emerges and remains in operation for five-plus years                                |

| Investment<br>(R&D, capital<br>expenditure,<br>mergers and<br>acquisitions,<br>venture capital) | >\$100 million<br>cumulatively<br>invested in<br>affiliated<br>technologies                                                                                                                                                                                                      | Value of investments doubles every other year (or year over year) for a five-year period, cumulatively exceeding \$250 million                                                                                                | <ul> <li>Investments drive consolidation or vertical integration</li> <li>Incumbent firms make substantial (\$100 million+) investments in the technology</li> </ul> | Government and industry coinvest to form public-private partnerships that explore technology maturation and commercialization |

Source: Author's creation.

The development of EUV met these conditions at different points in time:

- Novelty and coherence: The EUV community exhibited nascent signals of coherence early on, during the 1989 to 1993 period. While only about 15 EUV-affiliated publications appeared annually on average during this time, Intel committed \$200 million to EUV research in 1992, the research community harmonized on the term "EUV" in 1993 at a conference convened specifically for the topic, and the research community actually exceeded 300 contributors by the mid-1990s. Governments also formed the first EUV-focused public-private partnerships to explore the technology in earnest during this time, notably the U.S. National EUV Lithography Program and Europe's EXULT program.

- **Growth and impact:** The EUV community's rate of publication and investment demonstrated significant growth from 1997 to 2003. The number of named contributors on papers, a proxy for the size of the research community, doubled during this period. Likewise, the overall number of EUV-affiliated publications increased by 100 percent year over year, breaking 50 publications for the first time in 1998 according to Web of Science data. EUV-affiliated investments by major actors—which include mergers and acquisitions as well as R&D—also grew dramatically. ASML purchased SVG Lithography during this period.

### Protecting and Promoting the Next Emerging Technology

How did the most important emerging technology of the past 10 years, a technology that was largely pioneered in U.S. government labs and funded by Intel, end up monopolized by a Dutch company and sold to Intel's largest competitors first? The short answer to this question is that ASML had first-mover advantages, pursued strategic acquisitions, was able to weather cyclical downturns, enjoyed remarkable direct financial support from key customers, made a high-risk bet on an unproven technology (unlike its more conservative Japanese competitors), benefited from bad bets and competition among its rivals, and remained focused on its customers. Additionally, Intel stumbled.<sup>115</sup> Policy interventions had little to no impact on the timeline or maturation of EUV from roughly 2006 onward.

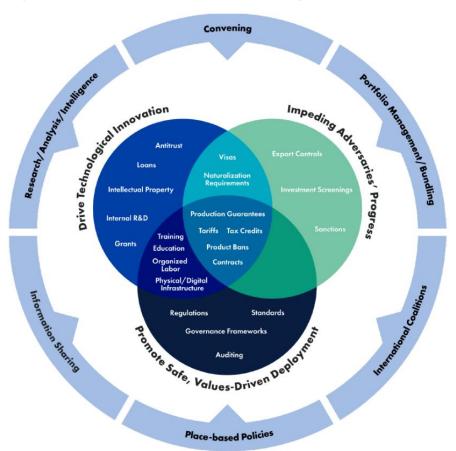

Answering this question more broadly has important implications for policymakers. Previous CSET research has detailed the trade-offs policymakers face when pursuing strategic technology and national security goals, especially with respect to driving technological innovation and impeding adversaries' progress (Figure 6).<sup>116</sup> The

development of EUV has several lessons for policymakers interested in promoting and protecting emerging technologies.

Figure 6. Policy Instruments and Enabling Levers

Source: Jack Corrigan, Melissa Flagg, and Dewey Murdick, "The Policy Playbook: Building a Systems-Oriented Approach to Technology and National Security Policy" (CSET, June 2023), <a href="https://cset.georgetown.edu/publication/the-policy-playbook/">https://cset.georgetown.edu/publication/the-policy-playbook/</a>.

### **Promoting Emerging Technology**

The story of EUV's emergence contains themes shared with other research agendas. Technologies often take decades to "emerge." These technologies grow, change, and mature in unexpected ways at a pace that either exceeds policymakers' abilities to productively intervene or is so slow that policymakers lose interest. International collaboration is inevitable (and desirable) when advancing complex, multifaceted research agendas. Government support—including direct financial support for public-private partnerships, indirect financial support, and funding basic science user facilities—is essential. Equally essential is partnership with the private sector, whose

support (in the form of large amounts of patient capital, technical know-how, and supplier-customer feedback loops) is necessary for commercializing an emerging technology. Collaborative development (and licensing) of IP can accelerate technology timelines, as can competition among private-sector actors.

The history of EUV suggests government intervention to promote emerging technologies is most valuable at early stages. This intervention can take several useful forms: retaining subject matter experts at national research facilities, endowing scientific user facilities with the resources necessary to pursue speculative high-risk high-reward research agendas, ensuring these facilities are open to international collaboration (either through direct access or the licensing of IP), direct financial support, creating public-private partnerships, facilitating information sharing, and convening otherwise-disparate research communities around specific topics for conferences or road mapping exercises.

With the benefit of hindsight, the single best policy the U.S. government pursued to promote EUV development was allowing national laboratory researchers engaged in EUV research to work with EUV LLC under the auspices of the virtual national lab from 1997 to 2003. However, EUV LLC only came into existence because Intel could afford to foot the bill at the time. Sustained government investment in basic and applied science user facilities also promoted EUV research. Importantly, these facilities convene academia and industry, remain open to worldwide collaboration, and offer nocost joint development projects to startups with strict IP protections and rights afforded to all participants. Finally, progress on large-scale scientific research agendas (such as those scoped by the National EUV Lithography Program, ASET, EUCLIDES, and EUV LLC) work best when given large amounts of patient capital: \$200 million to \$300 million per year for a five-to-ten-year period.<sup>117</sup>

### **Protecting Emerging Technology**

The primary mechanisms any government may use to protect a technology (research security, investment screening, export controls, and supply-chain security) are challenged by the nature of emerging technologies. Though governments can limit a technology's spread through guardrails that inhibit international collaboration or access to IP, stipulate who can and cannot invest in emerging technology firms, stop or interdict the international transfer of a technology, and assure strategically advantageous technology supply chains, emerging technologies are not so easily protected. Government technology protection regimes generally focus on ensuring economic or national security, and emerging technologies rarely present clear implications for these in their initial stages.

In some respects, the U.S. government made two key choices to "protect" EUV at a relatively early stage in its development via EUV LLC. First, the U.S. government effectively blocked Japanese lithography firms from direct participation in EUV LLC. Second, it permitted ASML's participation in EUV LLC, pursuant to provisions stipulating that ASML guarantee a certain amount of U.S.-based manufacturing and U.S.-origin content in its EUV tools. This latter requirement in particular guaranteed that the tools would contain enough U.S.-origin content to meet U.S. export-control thresholds. However, both of these decisions were not made by the U.S. government with explicit technology protection in mind but were rather a function of political pressure to ensure that taxpayer dollars would not be used to develop a technology that would ultimately be commercialized overseas.

The history of EUV shows that international collaboration and investment are essential and the ability to transfer technologies across borders is necessary for commercial sales as well as to source the highest quality components. Government efforts to protect emerging technologies run the risk of slowing down research and limiting firm profitability (and thus companies' ability to reinvest those profits in future R&D) at a time when a technology does not yet present clear economic or national security implications. Because nearly every emerging technology today is "dual use" (that is, it has commercial and potential military applications), efforts to protect these technologies run counter to the desires of the companies actively developing them in response to a perceived commercial opportunity.

This was particularly true in the case of EUV. Policymaker efforts to protect U.S.-origin innovations around EUV would have hampered overall development and disadvantaged U.S. firms such as Intel who were depending on the innovation. In fact, the primary reason ASML ended up in a monopoly position with respect to EUV technology is because of Intel. Intel assessed that SVG Lithography could not be relied on to supply an EUV system and therefore lobbied for its acquisition by ASML. Intel also argued for ASML's inclusion in EUV LLC. And Intel bet on ASML over its Japanese lithography rivals. U.S. efforts to protect EUV as an emerging technology would have run counter to Intel's stated goal: whoever could get EUV to market fastest was its preferred supplier, and only ASML fit the bill. Unfortunately, by the time EUV was ready for high-volume manufacturing, Intel's fabrication stumbles in transitioning from 14nm to 10nm and then 7nm semiconductors meant that EUV adoption actually added to its challenges rather than solved them. Only in 2023, five years after EUV's introduction in high-volume semiconductor manufacturing, did Intel starting to make use of the technology it first bet on 30 years ago. 118

### Conclusion

Like many other emerging technologies, EUV development required persistent collaboration and innovation between academia, industry, and government. This process is inherently global, resulting in a constant tension between government efforts to cooperatively promote and competitively protect a high-value technology. Promoting a technology requires early and sustained intervention and necessitates creative partnerships with industry. Protecting an emerging technology from specific competitor countries risks undermining innovation and frequently runs counter to the goals of the companies tasked with commercialization.

As a technology matures, government and industry priorities inevitably diverge: industry-led technology commercialization results in global supply chains and customer relationships that prioritize profit and reliability. Government efforts to control emergent technologies run risks ranging from ineffectual interventions to slowing innovation. The case of EUV highlights that there are no solutions, only tradeoffs, for policymakers who want to identify, protect, and promote the next emerging technology.

### Author

**John VerWey** is a nonresident fellow at CSET and an adviser at Pacific Northwest National Laboratory.

### Acknowledgments

For helpful feedback and suggestions, the author would like to thank Igor Mikolic-Torreira, Melissa Flagg, Autumn Toney, Taylore Roth, Kevin Boyack, Richard Klavans, Caleb Smith, Chris Miller, Chris Mack, James Dunham, and Rebecca Gelles. He would also like to thank Dale Brauner, Jahnavi Mukul, Shelton Fitch, Owen Daniels, and Liz Dana for editorial support.

© 2024 by the Center for Security and Emerging Technology. This work is licensed under a Creative Commons Attribution-Non Commercial 4.0 International License.

To view a copy of this license, visit <a href="https://creativecommons.org/licenses/by-nc/4.0/">https://creativecommons.org/licenses/by-nc/4.0/</a>.

Document Identifier: doi: 10.51593/20240003

# Appendix 1. Emerging Technology Attributes<sup>119</sup>

| Characteristic  | Concept                                         | Example       |

|-----------------|-------------------------------------------------|---------------|

| Radical novelty | Innovation that is clearly differentiated from  | Wireless      |

|                 | past technologies                               | communication |

|                 |                                                 | technologies  |

| Fast growth     | An increase in the number of actors, funding,   | Quantum       |

|                 | or outputs                                      | computing     |

| Coherence       | Convergence of previously separated research    | CRISPR-based  |

|                 | streams                                         | gene editing  |

| Prominent       | Potential to create an entirely new industry or | Google's      |

| impact          | fundamentally change an existing one            | PageRank      |

|                 |                                                 | algorithm     |

| Uncertainty or  | A variety of potential applications, but high-  | Biofuels      |

| ambiguity       | confidence future predictions are difficult     |               |

### Appendix 2. Next-Generation Lithography and Light Sources

Today's most advanced microelectronics have nearly atomic-level features. The ability to fabricate these microelectronics is a credit to EUV, and especially to the light source used in the system. The smaller the wavelength of light used to fabricate a chip, the smaller the features of that chip. As a result, the light source emerged as the single most challenging and consequential aspect of the entire NGL research agenda. This appendix summarizes the types of NGL technologies that were considered by industry from the nineties to the aughts, as well as the types of lithography light sources used by industry from the 1970s to present.

As discussed earlier in this paper, developing EUV required overcoming technical and economic obstacles. With respect to the light source used in EUV, this meant that not only did a new way of generating EUV light need to be invented, but the technology also needed to produce chips at volumes that made it profitable. This more or less doomed each of the other competing NGL technologies and light sources under consideration, as they were too expensive, too slow, or too complicated to operate reliably (Table 3).

Table 3. Next-Generation Lithography Approaches and Challenges<sup>120</sup>

| NGL                    | Challenge(s)                                                          |  |  |

|------------------------|-----------------------------------------------------------------------|--|--|

| Electron-beam          | Masks: Electrons absorbed in the mask deposit energy,                 |  |  |

| lithography (a.k.a. e- | causing it to heat up and distort, resulting in overlay errors.       |  |  |

| beam direct-write      | The scattering with angular limitation projection electron-           |  |  |

| lithography)           | beam lithography program attempted to mitigate this,                  |  |  |

|                        | without success.                                                      |  |  |

|                        | Exposure tool: Throughput (wafers processed per hour) is              |  |  |

|                        | limited due to beam current.                                          |  |  |

| Extreme ultraviolet    | <b>Optics</b> : Figure and finish (shape and purity) requirements of  |  |  |

| lithography            | mirrors are in the angstrom to sub-angstrom range. <sup>121</sup>     |  |  |

|                        | Essentially, the mirrors need to be atomically precise.               |  |  |

|                        | Mask: Extremely limited defect tolerance. Atomic-level                |  |  |

|                        | precision (30 angstrom) for multilayer coatings used to               |  |  |

|                        | make masks.                                                           |  |  |

|                        | <b>Light source</b> : EUV light is difficult to generate reliably and |  |  |

|                        | absorbed by nearly all standard materials and                         |  |  |

|                        | environments (including glass and air).                               |  |  |

| Ion projection         | <b>Light source</b> : Reliable ion sources are large and expensive.   |  |  |

| lithography            | <b>Exposure Tool</b> : Throughput (wafers processed per hour) is      |  |  |

|                        | limited due to beam current.                                          |  |  |

| X-ray proximity        | <b>Optics</b> : Lack of optics means changing image size to match     |  |  |

| lithography            | previously printed layers is challenging.                             |  |  |

|                        | Mask patterning: Mask features must be the same size as               |  |  |

|                        | the image being printed on wafer.                                     |  |  |

|                        | <b>Exposure tool</b> : Sub-100nm manufacturing results in             |  |  |

|                        | diffraction effects. Mitigation requires extremely precise            |  |  |

|                        | management of mask-to-wafer gap (the mask and wafer                   |  |  |

|                        | can only be a few microns apart) and pre-distortion of mask           |  |  |

|                        | patterns.                                                             |  |  |

Source: Author's compilation.

The semiconductor industry made continuous progress on the light sources used in lithography as ever-diminishing feature size necessitated light sources capable of generating shorter wavelengths (Figure 7).

Figure 7. Visible Light Spectrum

Source: ASML, "Light and Lasers," accessed June 26, 2024, <a href="www.asml.com/en/technology/lithography-principles/light-and-lasers">www.asml.com/en/technology/lithography-principles/light-and-lasers</a>.

Table 4 summarizes the commercial light sources and others that were considered for EUV lithography but ultimately abandoned in favor of the Cymer-developed carbon dioxide laser-produced plasma sources.

Table 4. Generations of Lithography Light Sources<sup>122</sup>

|            | Light Source               | Light Wavelength                         | Chip Feature Size     |

|------------|----------------------------|------------------------------------------|-----------------------|

|            | Mercury arc lamps          | G-line or "blue light" (436nm)           | 1 micron (1,000nm)    |

| Use        |                            | I-line or "invisible ultraviolet light," | 1 micron–220nm        |

|            |                            | (365nm)                                  |                       |

| erci       | Excimer lasers             | Krypton-fluoride based (248nm–           | 220nm-80nm            |

| й          |                            | 150nm)                                   |                       |

| Commercial |                            | Argon-fluoride based (193nm)             | 80nm-38nm             |

|            | Carbon-dioxide laser       | Tin-based plasma (13.5nm)                | 38nm–2nm (or lower)   |

|            | Free electron laser        | 1mm01nm                                  | N/A (not used in chip |

| ė,         |                            |                                          | fabrication)          |

| Use        | Steady-state microbunching | Unknown                                  | N/A (not used in chip |

| R&D        |                            |                                          | fabrication)          |

| ~          | Compact synchrotron laser  | Unknown                                  | N/A (not used in chip |

|            | source                     |                                          | fabrication)          |

Source: Author's compilation.

Appendix 3. Comparing EUV Publication Intensity between SPIE and Scopus/Web of Science, 1994–2017

### **Endnotes**

- <sup>1</sup> Clive Thompson, "Inside the Machine that Saved Moore's Law," *MIT Technology Review*, October 27, 2021, <u>www.technologyreview.com/2021/10/27/1037118/moores-law-computer-chips/</u>; Sander Hofman, "Making EUV: From Lab to Fab," ASML, March 30, 2022, <u>www.asml.com/en/news/stories/2022/making-euv-lab-to-fab.</u>